SiP设计能力

SiP設計能力

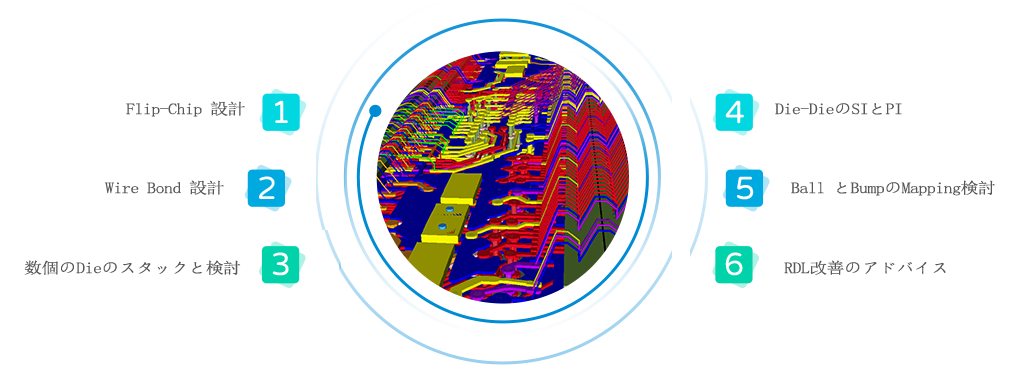

- チップ-パッケージ-システム連携計画と設計

- シミュレーションと設計の同期

- Wire Bond 3Dモデリング

- シミュレーションは高精度で、最適化は正確

- 主流のパッケージ基板製造プロセスに精通

- HspiceモデルはIBISモデルに切り替える

- 設計ガイダンスの生成を支援

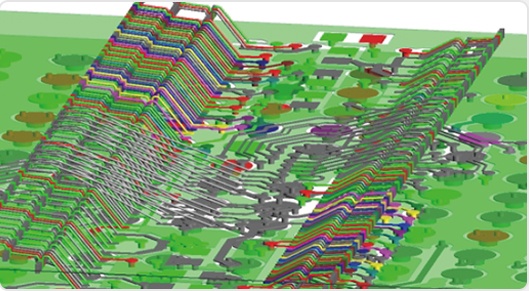

SiP設計案例の展示

- 9個 DDR4粒子、4+5層積層

- DDR4稼働レート3200Mbps

- SO-DIMMに匹敵する全体的な性能

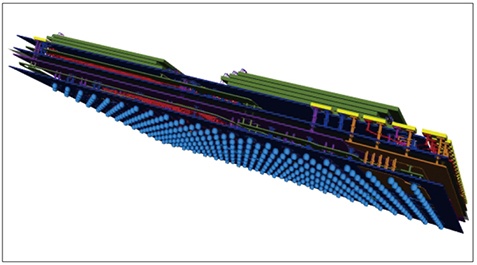

ATE能力紹介

- テスト対象のチップは、数千ピンまで、より多くのpinを持っています

- 最大40層以上積層し、板厚は5mm以上

- 引き回しと穴あけの設計と加工は、限界能力になる傾向があります

- 正確なシミュレーションは、配線がチップテストの精度に影響を与えないようにする必要があります